FPGA設計——正弦信號發(fā)生器-創(chuàng)新互聯(lián)

概述

成都創(chuàng)新互聯(lián)專注于企業(yè)營銷型網(wǎng)站建設、網(wǎng)站重做改版、廊坊網(wǎng)站定制設計、自適應品牌網(wǎng)站建設、H5頁面制作、商城建設、集團公司官網(wǎng)建設、成都外貿網(wǎng)站制作、高端網(wǎng)站制作、響應式網(wǎng)頁設計等建站業(yè)務,價格優(yōu)惠性價比高,為廊坊等各大城市提供網(wǎng)站開發(fā)制作服務。

FPGA具有高度實時的特性。這里討論基于FPGA設計一款簡單的正弦信號發(fā)生器。

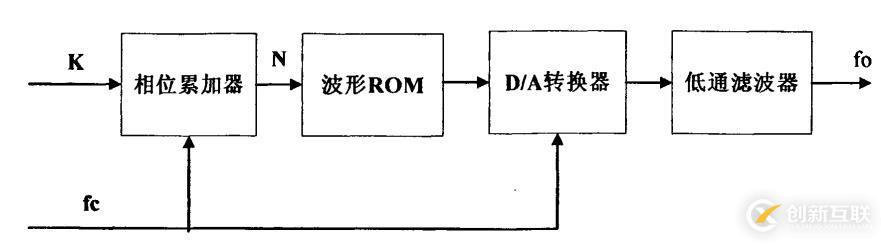

DDS原理

Direct Digital frequency Synthesis如下圖所示:

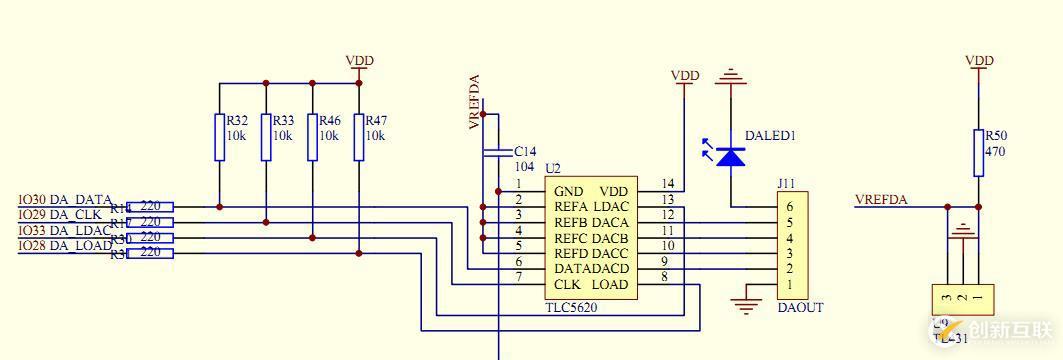

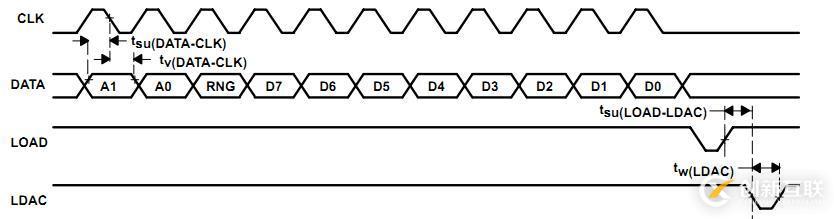

3. DAC原理

這里DAC采用TLC5620,下面分別給出DAC的原理圖和時序圖。

4. ROM文件的生成

ROM波形可以通過MIF或HEX文件保存在FPGA的ram或rom模塊中,也可以自己編寫HDL文件存儲。這里我們采用后者。

利用win-tc或matlab生產所需格式的函數(shù)數(shù)據(jù),參考C代碼如下:

#include "stdio.h"

#include "math.h"

#definePi 3.1416

#defineDEPTH 256

#defineLENTH DEPTH/2

intmain()

{

FILE*fp;

int j;

unsigned char i= 0;

unsigned char x= 0;

if((fp=fopen("d:\\sin.txt","w"))==NULL)

{

printf("can't open this file..\n");

exit(0);

}

for(j=0;j<DEPTH;j++)

{

x=(int)(LENTH+LENTH*sin(2*Pi*i/DEPTH - 0.5*Pi));

fprintf(fp," 'd%d: data = 'h%x;\n",i,x);

i++;

}

fprintf(fp,"\n");

fclose(fp);

printf("success\n");

return 0;

}5. DAC控制邏輯設計

module dac_ctrl( input clk, input rst_n, output reg dac_clk, output reg dac_load, output reg dac_ldac, output reg dac_dat, input [7:0] rom_dat, output reg [7:0] rom_addr, input [7:0] freq_ctrl ); //===================================== //The frequency of clk is divided by N parameter bitsize = 4; parameter N = 20; reg [bitsize:0] cnt0; always @(posedge clk or negedge rst_n) begin if(!rst_n) begin cnt0 <= 0; dac_clk <= 0; end else begin if(cnt0 < (N/2-1)) cnt0 <= cnt0 + 1'b1; else cnt0 <= 0; if(cnt0==0 && cnt1 >=1 && cnt1 <= 4'hb) dac_clk <= ~ dac_clk; else dac_clk <= dac_clk; end end wire clk_1M; assign clk_1M = (cnt0 == 0)?1'b1:1'b0; //====================================== reg [3:0] cnt1; always @(posedge clk or negedge rst_n) begin if(!rst_n) cnt1 <= 0; else if(clk_1M) cnt1 <= cnt1 + 1'b1; else cnt1 <= cnt1; end reg [7:0] cnt2; always @(posedge clk or negedge rst_n) begin if(!rst_n) cnt2 <= 0; else if(cnt1 == 4'hf) if(cnt2 != freq_ctrl) cnt2 <= cnt2 + 1'b1; else cnt2 <= 0; else cnt2 <= cnt2; end always @(posedge clk or negedge rst_n) begin if(!rst_n) rom_addr <= 0; else if(clk_1M && cnt1==4'hf && cnt2 == freq_ctrl) rom_addr <= rom_addr + 1'b1; else rom_addr <= rom_addr; end always @(cnt1) begin case(cnt1) 4'h2: begin dac_dat <= 1'b0; dac_load <= 1'b1; dac_ldac <= 1'b1; end 4'h3: begin dac_dat <= 1'b0; dac_load <= 1'b1; dac_ldac <= 1'b1; end 4'h4: begin dac_dat <= 1'b1; dac_load <= 1'b1; dac_ldac <= 1'b1; end 4'h5: begin dac_dat <= rom_dat[7]; dac_load <= 1'b1; dac_ldac <= 1'b1; end 4'h6: begin dac_dat <= rom_dat[6]; dac_load <= 1'b1; dac_ldac <= 1'b1; end 4'h7: begin dac_dat <= rom_dat[5]; dac_load <= 1'b1; dac_ldac <= 1'b1; end 4'h7: begin dac_dat <= rom_dat[4]; dac_load <= 1'b1; dac_ldac <= 1'b1; end 4'h8: begin dac_dat <= rom_dat[3]; dac_load <= 1'b1; dac_ldac <= 1'b1; end 4'h9: begin dac_dat <= rom_dat[2]; dac_load <= 1'b1; dac_ldac <= 1'b1; end 4'ha: begin dac_dat <= rom_dat[1]; dac_load <= 1'b1; dac_ldac <= 1'b1; end 4'hb: begin dac_dat <= rom_dat[0]; dac_load <= 1'b1; dac_ldac <= 1'b1; end 4'hc: begin dac_dat <= 1'b0; dac_load <= 1'b0; dac_ldac <= 1'b1; end 4'hd: begin dac_dat <= 1'bx; dac_load <= 1'b1; dac_ldac <= 1'b0; end default: begin dac_dat <= 1'bx; dac_load <= 1'b1; dac_ldac <= 1'b1; end endcase end endmodule

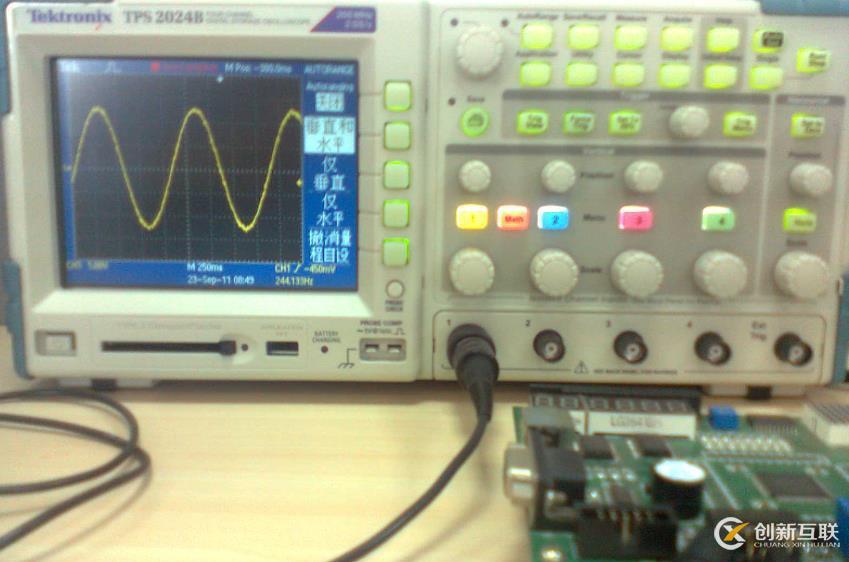

6. 測試結果

另外有需要云服務器可以了解下創(chuàng)新互聯(lián)scvps.cn,海內外云服務器15元起步,三天無理由+7*72小時售后在線,公司持有idc許可證,提供“云服務器、裸金屬服務器、高防服務器、香港服務器、美國服務器、虛擬主機、免備案服務器”等云主機租用服務以及企業(yè)上云的綜合解決方案,具有“安全穩(wěn)定、簡單易用、服務可用性高、性價比高”等特點與優(yōu)勢,專為企業(yè)上云打造定制,能夠滿足用戶豐富、多元化的應用場景需求。

名稱欄目:FPGA設計——正弦信號發(fā)生器-創(chuàng)新互聯(lián)

URL鏈接:http://www.chinadenli.net/article10/doecdo.html

成都網(wǎng)站建設公司_創(chuàng)新互聯(lián),為您提供網(wǎng)站內鏈、網(wǎng)站設計、ChatGPT、關鍵詞優(yōu)化、網(wǎng)站收錄、品牌網(wǎng)站設計

聲明:本網(wǎng)站發(fā)布的內容(圖片、視頻和文字)以用戶投稿、用戶轉載內容為主,如果涉及侵權請盡快告知,我們將會在第一時間刪除。文章觀點不代表本網(wǎng)站立場,如需處理請聯(lián)系客服。電話:028-86922220;郵箱:631063699@qq.com。內容未經(jīng)允許不得轉載,或轉載時需注明來源: 創(chuàng)新互聯(lián)

猜你還喜歡下面的內容

- EDU.CN網(wǎng)絡域名注冊方法,edu域名怎么注冊? 2019-11-15

- 域名隱私保護服務 避免域名注冊信息公示 2022-06-14

- 企業(yè)網(wǎng)站域名注冊備案的流程及提供資料 2021-03-31

- 域名注冊時常見的問題羅列 2022-03-03

- 小程序開發(fā)中如果選擇域名注冊和云服務器 2021-03-03

- 關于網(wǎng)站域名注冊和國際國內域名的問題解答 2022-08-15

- 域名注冊要考慮的四大因素 2015-06-24

- 域名注冊建議 2022-07-28

- 域名注冊后備案要注銷該怎么操作? 2023-03-26

- .co域名注冊有哪些優(yōu)勢 2016-11-01

- 這個域名注冊不到十天就啟動上線 2022-08-02

- .Co域名注冊規(guī)則 2022-06-07